## Please cite the Published Version

Hashmi, Adeel (2011) Hardware Acceleration of Network Intrusion Detection System Using FPGA. Doctoral thesis (PhD), Manchester Metropolitan University.

## Downloaded from: https://e-space.mmu.ac.uk/626461/

Usage rights: Creative Commons: Attribution-Noncommercial-Share Alike

## Enquiries:

If you have questions about this document, contact openresearch@mmu.ac.uk. Please include the URL of the record in e-space. If you believe that your, or a third party's rights have been compromised through this document please see our Take Down policy (available from https://www.mmu.ac.uk/library/using-the-library/policies-and-guidelines)

# MANCHESTER METROPOLITAN UNIVERSITY

# Hardware Acceleration of Network Intrusion Detection System Using FPGA

by

# Adeel Hashmi

A thesis submitted in partial fulfillment for the degree of Doctor of Philosophy

in the Faculty of Science and Engineering School of Computing, Mathematics and Digital Technology

January 2011

# Acknowledgements

I would like to express my gratitude to my PhD supervisors Dr. Andy Nisbet and Mr. Clive Mingham for the guidance and support. Throughout my thesis writing period, they provided encouragement, sound advice, good teaching, and lots of good ideas. I would have been lost without them.

I am grateful to my office mates for providing a stimulating and fun environment in which to learn and grow. I am especially grateful to Pete, Naomi and John for their valuable feedbacks and providing me regular cups of coffee.

Special thanks to my friends Nauman and Kaleem for helping me get through the difficult times, and for all the emotional support, entertainment, and caring they provided.

Lastly, and most importantly, I wish to thank my family for their support, patience and understanding. To them I dedicate this thesis.

# Abstract

This thesis presents new algorithms and hardware designs for Signature-based Network Intrusion Detection System (SB-NIDS) optimisation exploiting a hybrid hardwaresoftware co-designed embedded processing platform. The work describe concentrates on optimisation of a complete SB-NIDS *Snort* application software on a FPGA based hardware-software target rather than on the implementation of a single functional unit for hardware acceleration. Pattern Matching Hardware Accelerator (PMHA) based on Bloom filter was designed to optimise SB-NIDS performance for execution on a Xilinx MicroBlaze soft-core processor. The Bloom filter approach enables the potentially large number of network intrusion attack patterns to be efficiently represented and searched primarily using accesses to FPGA on-chip memory. The thesis demonstrates, the viability of hybrid hardware-software co-designed approach for SB-NIDS. Future work is required to investigate the effects of later generation FPGA technology and multi-core processors in order to clearly prove the benefits over conventional processor platforms for SB-NIDS.

The strengths and weaknesses of the hardware accelerators and algorithms are analysed, and experimental results are examined to determine the effectiveness of the implementation. Experimental results confirm that the PMHA is capable of performing network packet analysis for gigabit rate network traffic. Experimental test results indicate that our SB-NIDS prototype implementation on relatively low clock rate embedded processing platform performance is approximately 1.7 times better than Snort executing on a general purpose processor on PC when comparing processor cycles rather than wall clock time.

# Contents

| A             | cknov | wledge        | ements                                               | i                      |

|---------------|-------|---------------|------------------------------------------------------|------------------------|

| A             | bstra | $\mathbf{ct}$ |                                                      | ii                     |

| Li            | st of | Figur         | es                                                   | vi                     |

| $\mathbf{Li}$ | st of | Table         | S                                                    | $\mathbf{i}\mathbf{x}$ |

| A             | bbre  | viation       | lS                                                   | x                      |

| 1             | Intr  | oduct         | ion                                                  | 1                      |

|               | 1.1   | Backg         | round and Problem Overview                           | 1                      |

|               | 1.2   |               | on Synopsis                                          | 2                      |

|               | 1.3   |               | and Objectives                                       | 3                      |

|               |       | 1.3.1         | Objectives                                           | 3                      |

|               | 1.4   | Contr         | ibutions and Claims                                  | 4                      |

|               | 1.5   |               | s Outline                                            | 6                      |

| <b>2</b>      | Bac   | kgrou         | nd                                                   | 7                      |

|               | 2.1   | 0             | er Roadmap                                           | 7                      |

|               | 2.2   | -             | ork Security Issues                                  | 8                      |

|               |       | 2.2.1         | Flawed Internet Protocol Design                      | 9                      |

|               |       | 2.2.2         | Vulnerabilities in Software                          | 21                     |

|               |       | 2.2.3         | Malicious Code                                       | 22                     |

|               | 2.3   | Netwo         | ork Defence Mechanism                                | 25                     |

|               |       | 2.3.1         | Configuration Management                             | 25                     |

|               |       | 2.3.2         | Firewall                                             | 25                     |

|               |       | 2.3.3         | Intrusion Detection System                           | 27                     |

|               | 2.4   | Intrus        | ion Detection System: An Indepth Analysis            | 28                     |

|               |       | 2.4.1         | Host Monitoring                                      | 28                     |

|               |       | 2.4.2         | Network Monitoring                                   | 28                     |

|               |       | 2.4.3         | Types of Intrusion Detection System                  | 28                     |

|               |       | 2.4.4         | Intrusion Detection Techniques                       | 32                     |

|               |       | 2.4.5         | Popular Intrusion Detection System Products          | 33                     |

|               |       | 2.4.6         | Issues and Limitations of Intrusion Detection System | 34                     |

|               |       | 2.4.7         | NIDS Computationally Demanding Process               | 36                     |

|               | 2.5   |               | ary                                                  | 39                     |

| 3        | $\mathbf{Sur}$ | vey and Related Work                                                                                           | 40    |

|----------|----------------|----------------------------------------------------------------------------------------------------------------|-------|

|          | 3.1            | Chapter Roadmap                                                                                                | . 40  |

|          | 3.2            | Introduction to Literature Review                                                                              | . 41  |

|          | 3.3            | Literature Explanation                                                                                         | . 41  |

|          | 3.4            | SB-NIDS using High Performance Computing Platform                                                              | . 41  |

|          |                | 3.4.1 Computer Clusters for SB-NIDS                                                                            | . 44  |

|          |                | 3.4.2 Embedded Processing Platform for NIDS                                                                    | . 50  |

|          | 3.5            | Pattern Matching for SB-NIDS                                                                                   | . 53  |

|          |                | 3.5.1 SB-NIDS Specific Pattern Matching Algorithms                                                             | . 54  |

|          |                | 3.5.2 Packet Filtering Technique for Pattern Matching in SB-NIDS                                               | . 58  |

|          |                | 3.5.3 Pattern matching using High Performance Computing Platform .                                             | . 68  |

|          | 3.6            | Chapter Summary                                                                                                | . 74  |

| <b>4</b> | Pro            | posed System Architecture                                                                                      | 75    |

|          | 4.1            | Chapter Roadmap                                                                                                | . 75  |

|          | 4.2            | System Description                                                                                             | . 76  |

|          |                | 4.2.1 Overview                                                                                                 | . 76  |

|          |                | 4.2.2 Architecture                                                                                             | . 76  |

|          |                | 4.2.3 Deployment                                                                                               | . 77  |

|          |                | 4.2.4 Features                                                                                                 | . 77  |

|          | 4.3            | System Prototyping                                                                                             | . 79  |

|          |                | 4.3.1 Snort                                                                                                    | . 79  |

|          |                | 4.3.2 Snort Architecture                                                                                       | . 80  |

|          |                | 4.3.3 Prototyping Challenges                                                                                   | . 85  |

|          |                | 4.3.4 Prototyping Requirements                                                                                 | . 86  |

|          | 4.4            | Chapter Summary                                                                                                | . 91  |

| <b>5</b> | Des            | sign and Implementation                                                                                        | 92    |

|          | 5.1            | Chapter Roadmap                                                                                                | . 92  |

|          | 5.2            | Snort Port on Hybrid Hardware-Software Processing Platform (MMU-                                               |       |

|          |                | Snort I)                                                                                                       | . 93  |

|          |                | 5.2.1 Analysis $\ldots$       | . 93  |

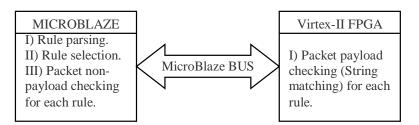

|          |                | 5.2.2 Design $\ldots$         | . 94  |

|          |                | 5.2.3 Implementation $\ldots$ | . 97  |

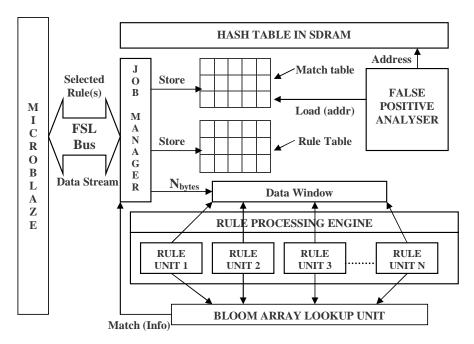

|          | 5.3            | Pattern Matching Hardware Accelerator (MMU-Snort II)                                                           | . 99  |

|          |                | 5.3.1 Analysis                                                                                                 | . 100 |

|          |                | 5.3.2 Design $\ldots$         | . 106 |

|          |                | 5.3.3 Implementation $\ldots$ | . 114 |

|          | 5.4            | Final Optimisation of Snort Port (MMU-Snort III)                                                               | . 118 |

|          |                | 5.4.1 Analysis $\ldots$       | . 118 |

|          |                | 5.4.2 Design $\ldots$                                                                                          | . 123 |

|          | 5.5            | Chapter Summary                                                                                                | . 128 |

| 6        | Res            | sults and Analysis                                                                                             | 129   |

|          | 6.1            | Chapter Roadmap                                                                                                | . 129 |

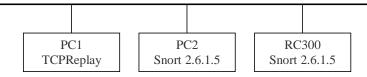

|          | 6.2            | Experimental Testbed                                                                                           | . 130 |

|          | 6.3            | Testing and Evaluation of Snort Port (MMU-Snort I)                                                             | . 131 |

|   |     | 6.3.1 Functional Test                                                 | L |

|---|-----|-----------------------------------------------------------------------|---|

|   |     | 6.3.2 Performance Test                                                | L |

|   | 6.4 | Testing and Evaluation of Pattern Matching Hardware Accelerator (MMU- |   |

|   |     | Snort II and MMU-Snort III)                                           | j |

|   |     | 6.4.1 Performance Test                                                | j |

|   |     | 6.4.2 Comparison with Previous Work                                   | 3 |

|   | 6.5 | Chapter Summary                                                       | F |

| 7 | Con | clusion and Future Work 145                                           | 5 |

|   | 7.1 | Chapter Summary                                                       | j |

|   | 7.2 | Overall Conclusion                                                    | ) |

|   | 7.3 | Limitations and Future Directions                                     | ) |

|   |     | 7.3.1 Regular Expression Search                                       | ) |

|   |     | 7.3.2 Non-Interruptible Update                                        | L |

|   |     | 7.3.3 Packet filtering                                                | ) |

|   |     | 7.3.3 Packet filtering                                                |   |

# Bibliography

**APPENDIX A:** Published Research

166

154

# List of Figures

| 2.1        | Two core reasons of network attacks                                        | 8        |

|------------|----------------------------------------------------------------------------|----------|

| 2.2        | Denial of Service classification                                           | 10       |

| 2.3        | Denial of Service second classification                                    | 10       |

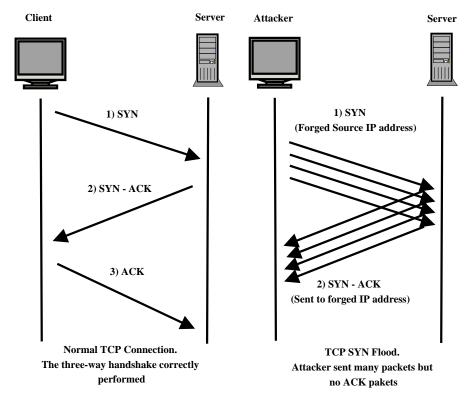

| 2.4        | Denial of Service attacks using TCP                                        | 11       |

| 2.5        | Normal TCP connection and TCP SYN flooding attack                          | 12       |

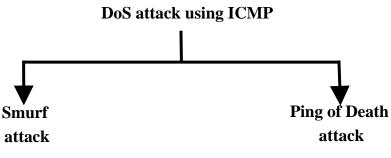

| 2.6        | Denial of Service attacks using ICMP                                       | 13       |

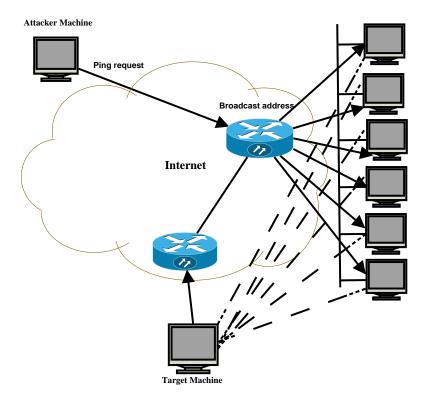

| 2.7        | Smurf attack                                                               | 14       |

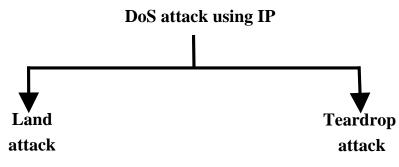

| 2.8        | Denial of Service attacks using IP                                         | 15       |

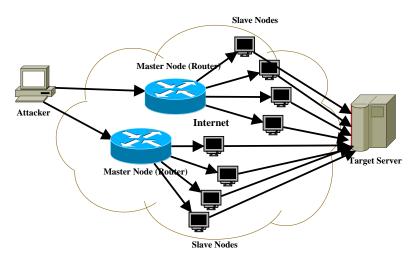

| 2.9        | Network topology of DDoS                                                   | 17       |

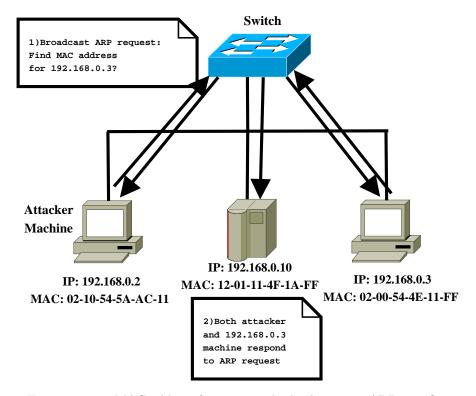

| 2.10       | MAC address forgery attack also known as ARP spoofing                      | 19       |

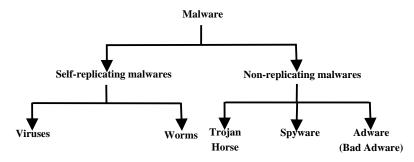

| 2.11       | Types of malware                                                           | 23       |

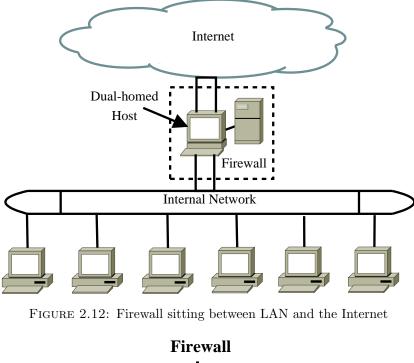

| 2.12       | Firewall sitting between LAN and the Internet                              | 26       |

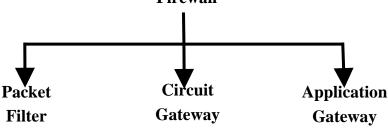

| 2.13       | Types of Firewall                                                          | 26       |

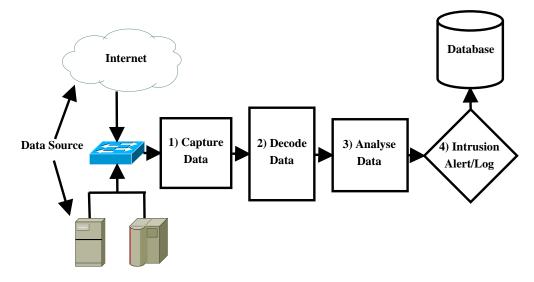

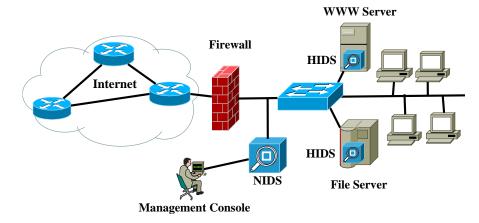

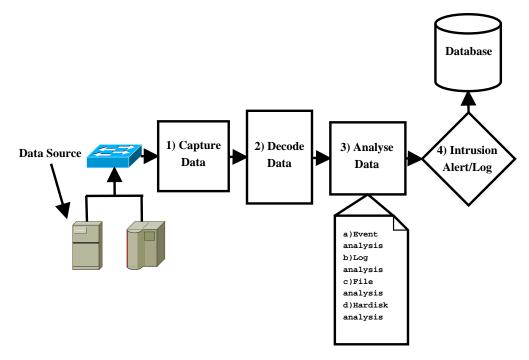

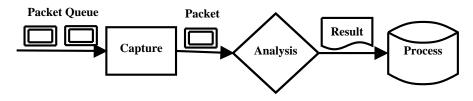

| 2.14       | Typical IDS data analyses flow                                             | 27       |

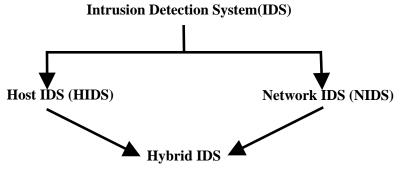

| 2.15       | Types of IDS                                                               | 29       |

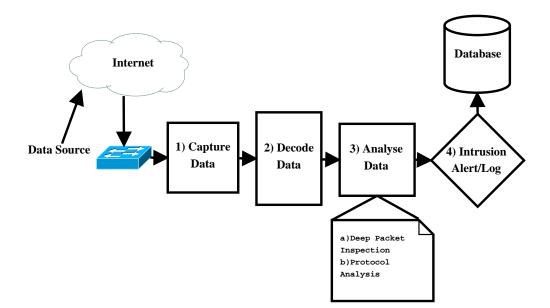

| 2.16       | Typical NIDS data analyses flow                                            | 30       |

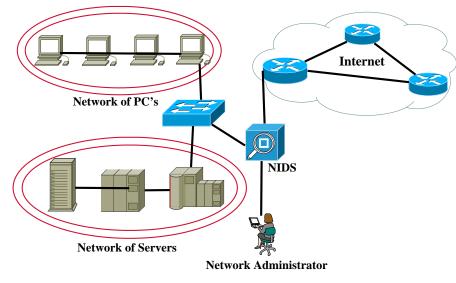

| 2.17       | NIDS sitting between LAN and the Internet                                  | 30       |

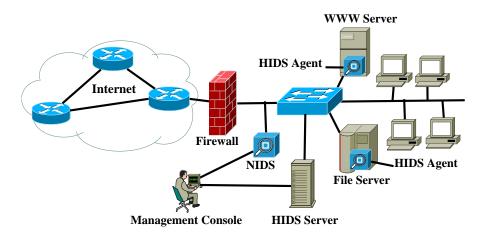

| 2.18       | Typical HIDS data analyses flow                                            | 31       |

| 2.19       | NIDS sitting between LAN and the Internet and HIDS agents on Internet      |          |

|            | facing servers                                                             | 32       |

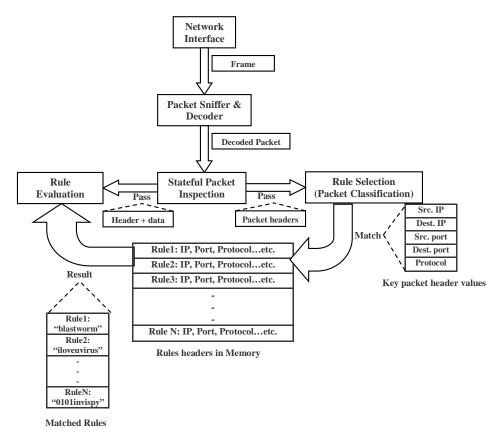

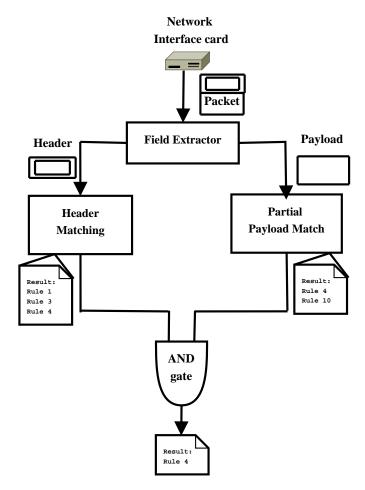

| 2.20       | Packet Inspection in SB-NIDS                                               | 37       |

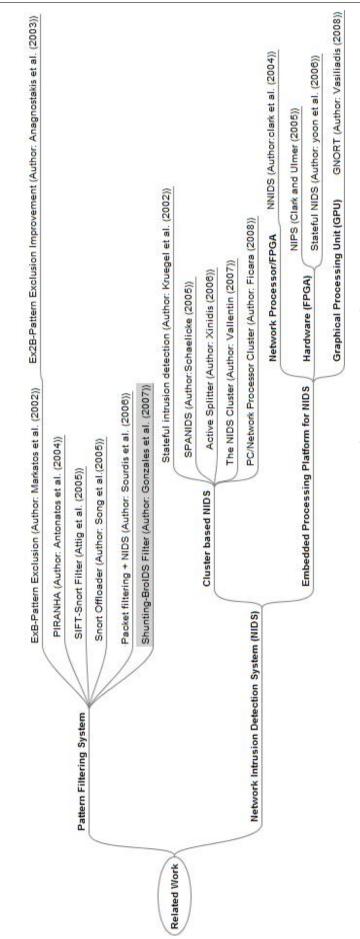

| 3.1        | Network Intrusion Detection Systems and Filtering Systems                  | 42       |

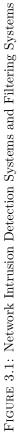

| 3.1<br>3.2 | Pattern Matching                                                           | 42<br>43 |

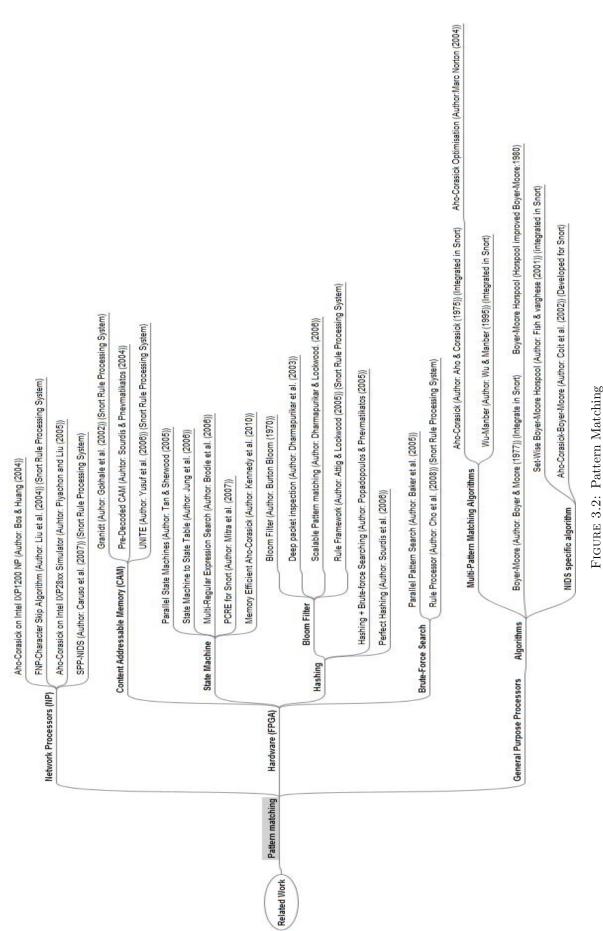

| 3.3        | Typical arrangement of hardware for Cluster-based SB-NIDS                  | 45<br>45 |

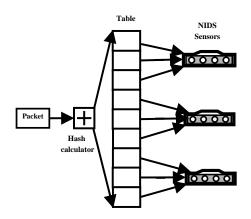

| 3.4        | Loadbalancing using hash calculator                                        | 47       |

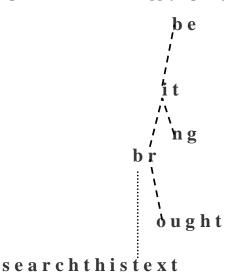

| 3.4        | Suffix tree and Bad-character shift table for SBMH                         | 55       |

| 3.6        | Example showing pattern search in a text "patternrstyz". Pattern "rstyz"   | 00       |

| 0.0        | is found in a text in final shift                                          | 55       |

| 3.7        | Prefix tree and text alignment to begin pattern search in AC-BM algorithm  |          |

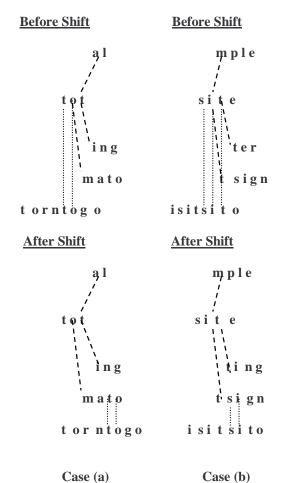

| 3.8        | Search shows good-prefix shift                                             | 57       |

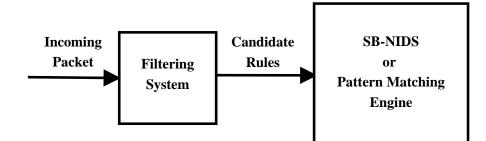

|            | Block diagram showing typical position of Filtering System for SB-NIDS .   |          |

|            | Pre-processing in ExB of a text "1000poundsinnetworkpacket"                | 60       |

|            | ExB algorithm searching patterns in a text "1000poundsinnetworkpacket"     | 60       |

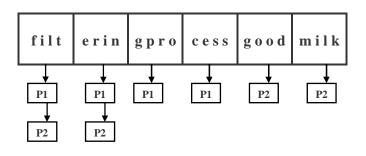

|            | Example of pre-processing of patterns "filteringprocess" and "filterin-    |          |

|            | goodmilk" in PIRAMHA                                                       | 62       |

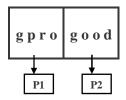

| 3.13       | Example of searching text "verygoodfilteringprocess" for patterns "filter- |          |

|            | ingprocess" and "filteringoodmilk" in PIRAMHA                              | 62       |

|            |                                                                            |          |

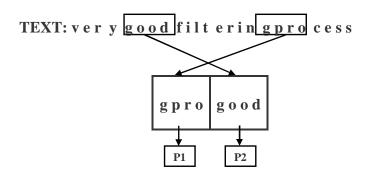

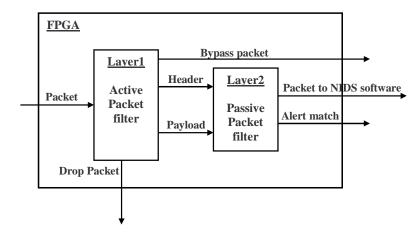

|      | Block diagram of Snort offloader showing two main hardware modules<br>Packet processing flow in filtering hardware |       |

|------|--------------------------------------------------------------------------------------------------------------------|-------|

| 4.1  | NIDS Modules                                                                                                       | . 76  |

| 4.2  | NIDS Deployment                                                                                                    |       |

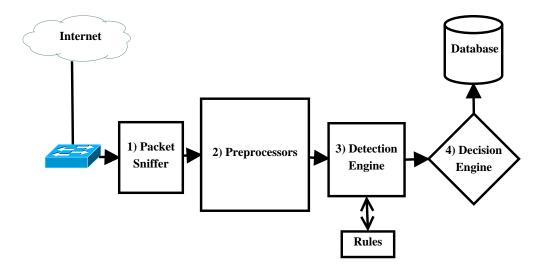

| 4.3  | Snort architecture showing packet processing flow                                                                  |       |

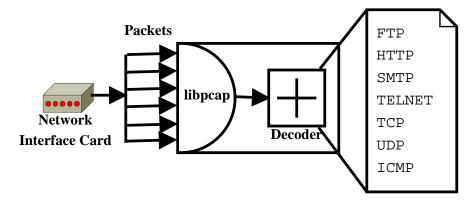

| 4.4  | Packet Sniffer function                                                                                            |       |

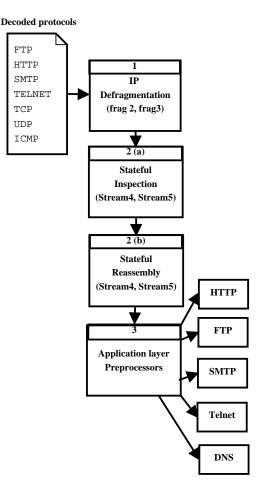

| 4.5  | Packet processing flow through Preprocessors                                                                       |       |

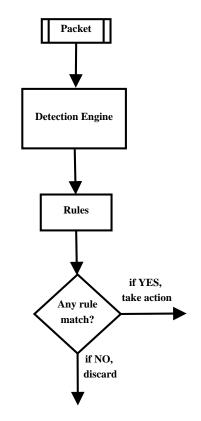

| 4.6  | Packet checking in Detection Engine                                                                                |       |

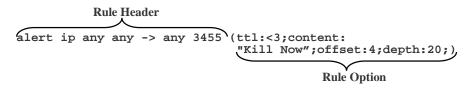

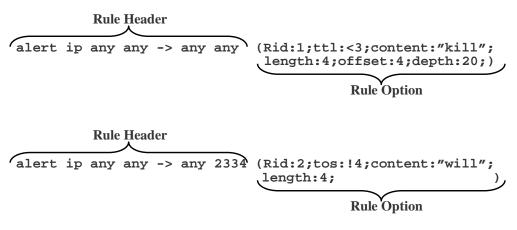

| 4.7  | Snort rule of CGI-PHF attack                                                                                       |       |

| 4.8  | Snort rule header                                                                                                  |       |

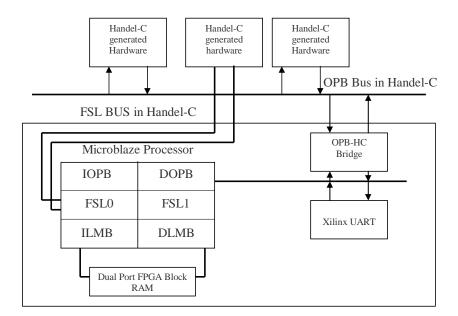

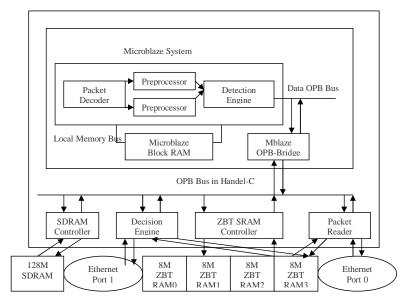

| 4.9  | HandelC and MicroBlaze design system                                                                               |       |

| 4.10 |                                                                                                                    |       |

| 4.11 |                                                                                                                    |       |

|      |                                                                                                                    |       |

| 5.1  | Snort on RC300 board                                                                                               |       |

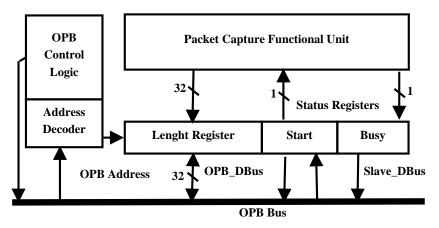

| 5.2  | Packet Capture Hardware Accelerator (PCHA) architecture                                                            |       |

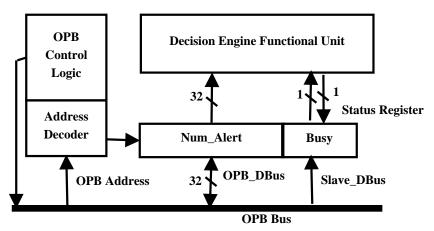

| 5.3  | Decision Engine Hardware Accelerator (DEHA) architecture                                                           |       |

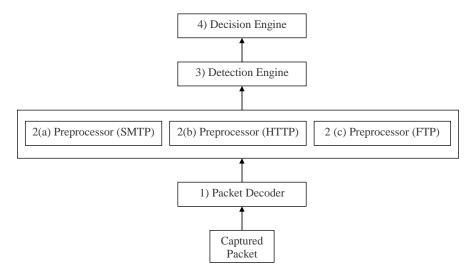

| 5.4  | Key Stages of Snort                                                                                                |       |

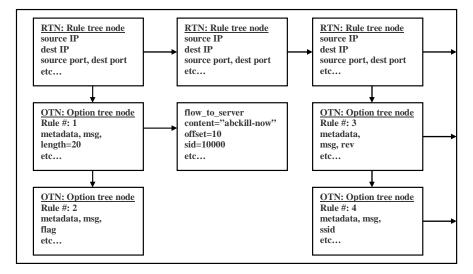

| 5.5  | Parsed structure of Snort rules in memory (SRT)                                                                    |       |

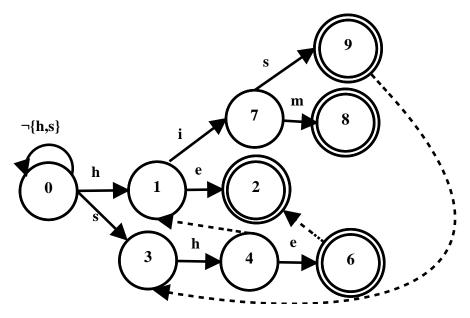

| 5.6  | A state machine concept constructed using patterns "he, she, him, her, his"                                        |       |

| 5.7  | Example Snort rule                                                                                                 |       |

| 5.8  | Python code: 3 character string to integer conversion                                                              |       |

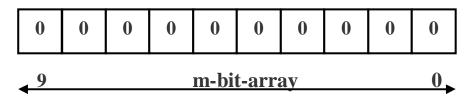

| 5.9  | Empty Bloom Filter                                                                                                 |       |

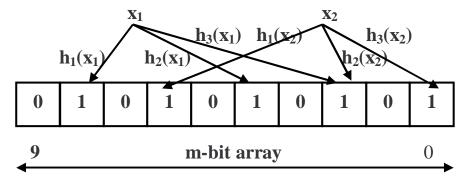

|      | Insert bit-strings $(x_1)$ and $(x_2)$                                                                             |       |

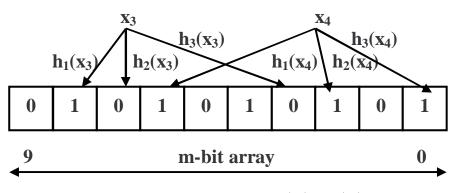

|      | Query bit-strings $(x_3)$ and $(x_4)$                                                                              |       |

|      | Top level diagram showing modified Detection Engine                                                                |       |

|      | Block diagram of pattern matching hardware function unit                                                           |       |

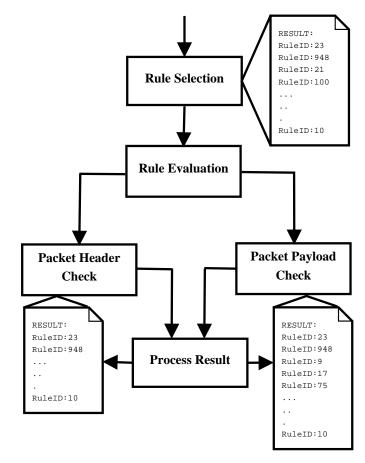

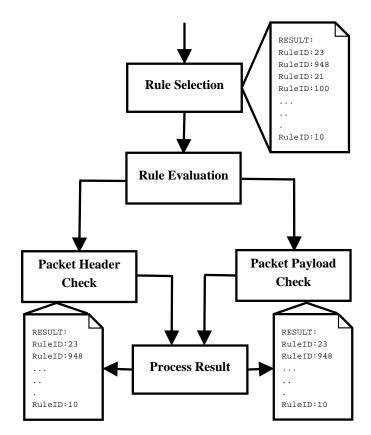

|      | Packet processing flow for Snort rule evaluation                                                                   |       |

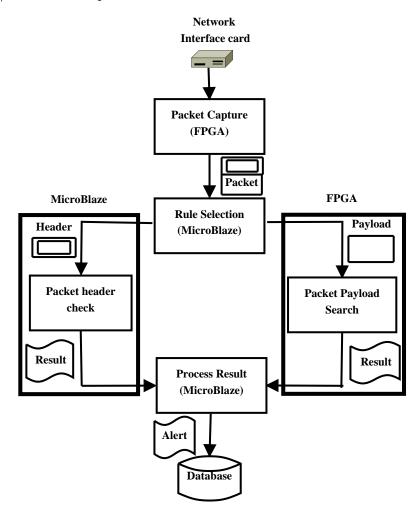

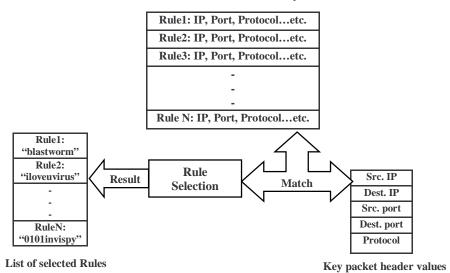

|      | Rule selection                                                                                                     |       |

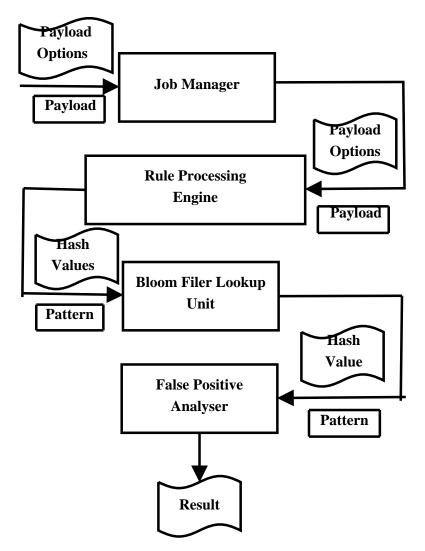

|      | Hardware modules performing packet payload searching                                                               |       |

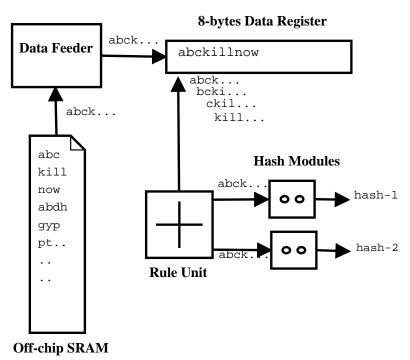

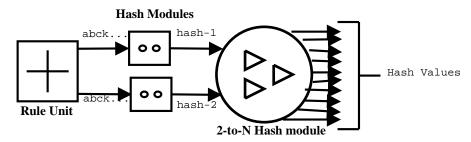

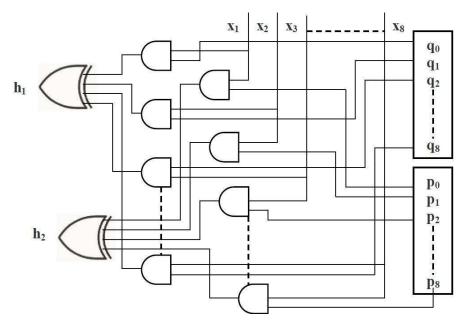

| 5.17 | Rule units computing hash values                                                                                   | 112   |

| 5.18 | 2-to-N hash module computing ten hash values using two hash values                                                 | . 113 |

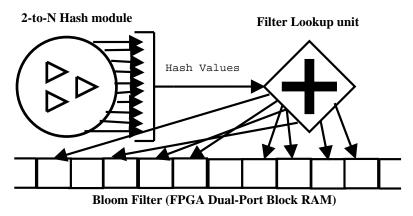

| 5.19 | Bloom filter index checking with corresponding hash values                                                         | 113   |

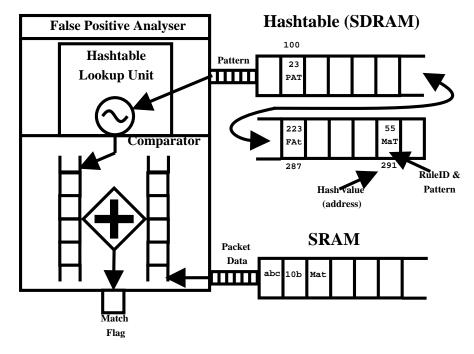

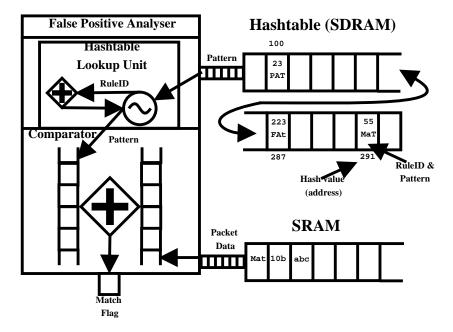

|      | False positive analyser with hash table lookup unit and comparator circuit                                         |       |

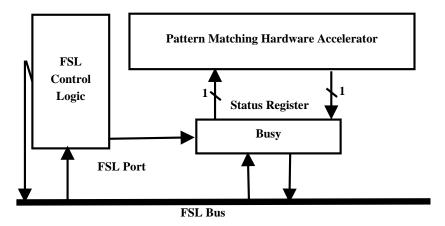

|      | Pattern Matching Hardware Accelerator (PMHA) architecture                                                          |       |

|      | Hash calculator circuit design                                                                                     |       |

| 5.23 | Rule selection and evaluation result                                                                               | 120   |

|      | Example Snort rules                                                                                                |       |

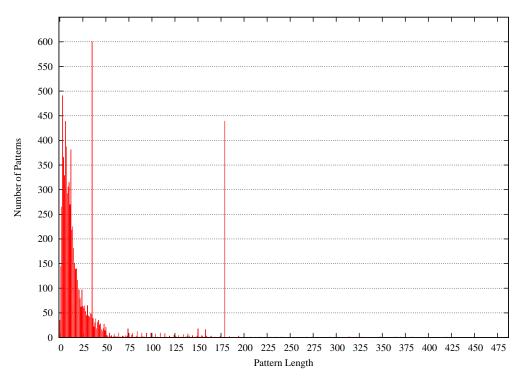

| 5.25 | Patterns from Snort rules with their length                                                                        | 122   |

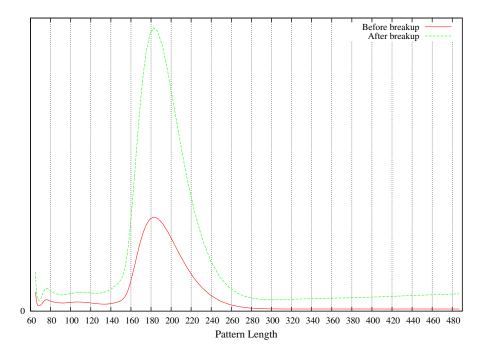

| 5.26 | A line graph showing the increase of patterns after breakup                                                        | 123   |

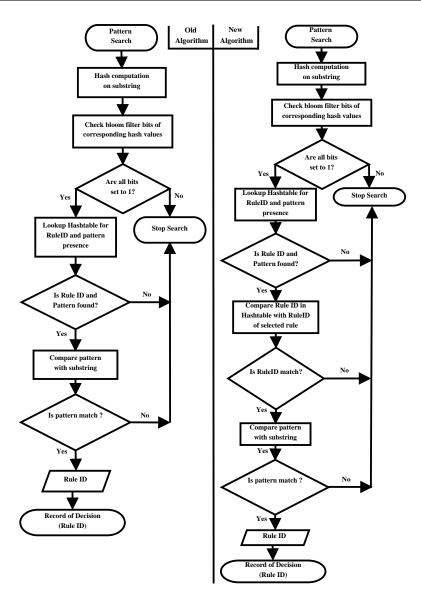

| 5.27 | Old and new Pattern Matching algorithms on FPGA                                                                    | 124   |

| 5.28 | Rule selection and evaluation result with modified algorithm                                                       | 125   |

| 5.29 | Modified false positive analyser with Hash table lookup unit and Com-                                              | 100   |

| F 90 | parator circuit                                                                                                    |       |

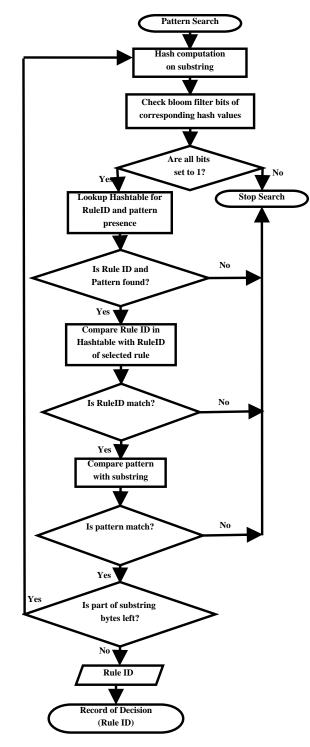

| 5.30 | Pattern matching algorithm flowchart for longer (> 64 bytes) pattern $\therefore$                                  |       |

| 6.1  | Topology of experimental test network                                                                              | 130   |

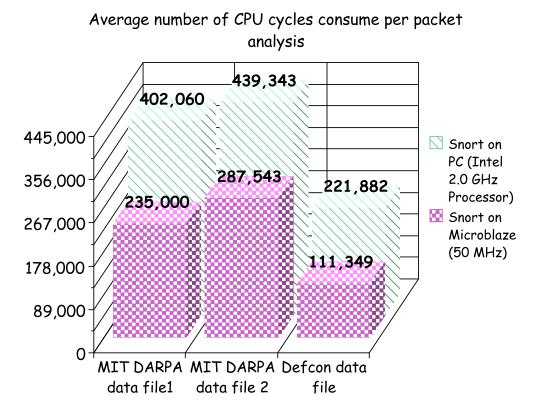

| 6.2  | Snort CPU cycles comparison                                                                       |

|------|---------------------------------------------------------------------------------------------------|

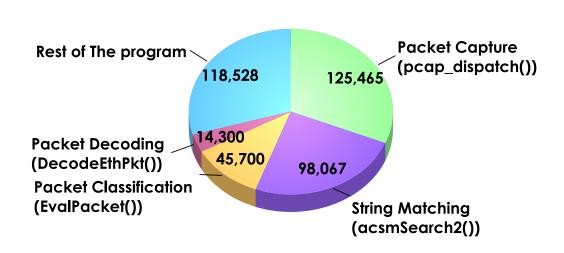

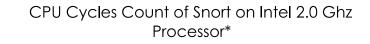

| 6.3  | CPU cycles count of Snort on PC                                                                   |

| 6.4  | CPU cycles count of Snort on MicroBlaze                                                           |

| 6.5  | Synthesis result on Xilinx XC2V6000 -4 Virtex-II FPGA                                             |

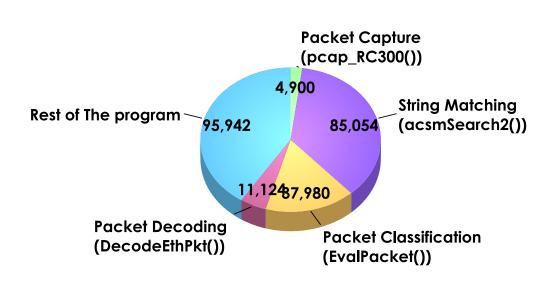

| 6.6  | Aho-Corasick state machine and pattern matching hardware accelerator                              |

|      | memory requirements                                                                               |

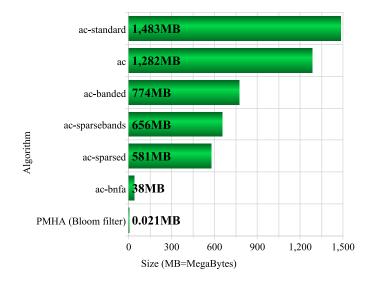

| 6.7  | Aho-Corasick (ac-standard) state machine memory size (MB) for different                           |

|      | character count                                                                                   |

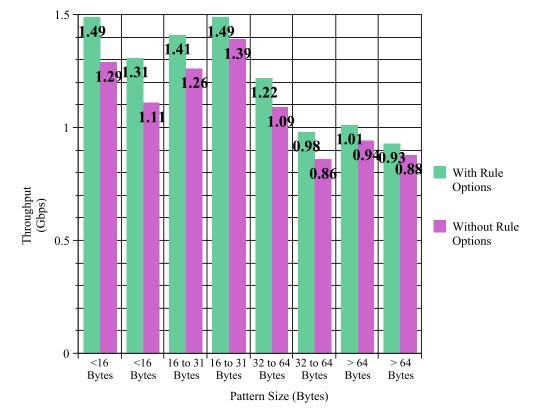

| 6.8  | PMHA throughput at 50 MHz for the test results in Table $6.1$ 137                                 |

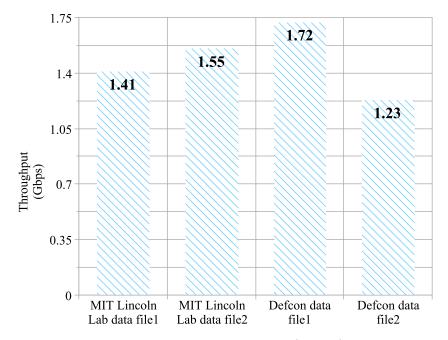

| 6.9  | Pattern Matching Hardware Accelerator (PMHA) throughput with total                                |

|      | 7876 patterns                                                                                     |

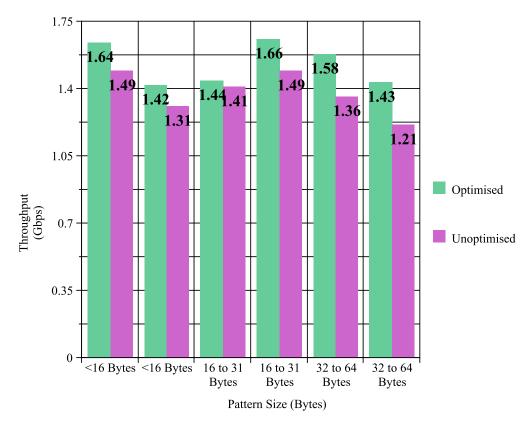

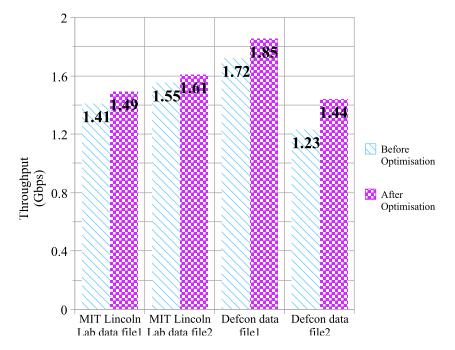

| 6.10 | PMHA throughput comparison before and after optimisation $\ldots\ldots\ldots$ . 139               |

| 6.11 | PMHA throughput comparison before and after optimisation $\ . \ . \ . \ . \ . \ . \ . \ . \ . \ $ |

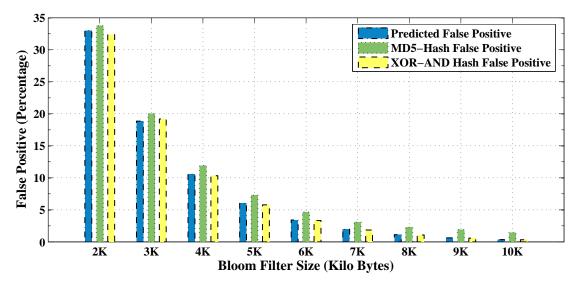

| 6.12 | False Positive vs Bloom filter size                                                               |

| 6.13 | Synthesis result of six hash module on Xilinx XC2V6000 -4 Virtex-II FPGA142 $$                    |

| 6.14 | Synthesis result of two hash module and 2-to-N hash module on Xilinx                              |

|      | XC2V6000 -4 Virtex-II FPGA                                                                        |

| 6.15 | Synthesis result of full SB-NIDS prototype (MMU-Snort III) on Xilinx                              |

|      | XC2V6000 - 4 Virtex-II FPGA                                                                       |

# List of Tables

| 2.1  | Summary of DoS attacks using TCP                                                |

|------|---------------------------------------------------------------------------------|

| 2.2  | Summary of DoS attacks using ICMP 13                                            |

| 2.3  | Summary of DoS attacks using IP 10                                              |

| 2.4  | Common DDoS attack tools                                                        |

| 2.5  | Forgery using Network protocols                                                 |

| 2.6  | Viruses types and behaviour                                                     |

| 2.7  | Comparison of IDS types 29                                                      |

| 2.8  | Summary of IDS detection techniques                                             |

| 2.9  | Summary: Product details of leading HIDS and NIDS 34                            |

| 2.10 | Summary: Best NIDS/NIPS product of leading private companies 34                 |

| 3.1  | Summary of Computer cluster and Embedded processing based SB-NIDS 44            |

| 3.2  | NIDS cluster hardware specification 40                                          |

| 3.3  | Advantages and disadvantages of cluster based NIDS                              |

| 3.4  | NIDS specific hybrid multi-pattern matching algorithms                          |

| 3.5  | Pattern Filtering Systems                                                       |

| 3.6  | Details of Hardware technologies                                                |

| 3.7  | Advantages and disadvantages of software based pattern matching filter-         |

|      | ing system                                                                      |

| 3.8  | Hardware based pattern filtering                                                |

| 3.9  | Some pattern matching implementation on FPGA and Network Processor 69           |

| 3.10 | Hardware Details of development platform                                        |

| 3.11 | Snort Rule Evaluation Systems summary                                           |

| 4.1  | Modifier Keywords                                                               |

| 5.1  | Profile of Snort on PC                                                          |

| 5.2  | Total number of patterns                                                        |

| 6.1  | Clock cycle count of Pattern Matching Hardware Accelerator (PMHA) $13^{\prime}$ |

| 6.2  | Comparison of clock cycle count of PMHA before and after optimisation . $139$   |

| 6.3  | False positive rate of PMHA (MMU-SnortII) with 7876 patterns 14                 |

| 6.4  | False positive rate of PMHA (MMU-Snort III) with 9150 patterns 142              |

| 6.5  | Pattern Matching Hardware Accelerator (PMHA) Memory Size (Kbits) . 143          |

| 6.6  | Pattern matching hardware architecture on FPGA                                  |

# Abbreviations

| ARPAddress Resolution ProtocolASICApplication Specific Integrated CircuitASIPApplication-Specific Instruction-set ProcessorBGPBorder Gateway ProtocolBMBoyer-MooreBRAMBlock Random Access MemoryCAMContent Addressable MemoryCERTComputer Emergency Response TeamCIACComputer Incident Advisory CapabilityCPUCentral Processing UnitDEHADecision Engine Hardware AcceleratorDoSDenial of ServiceDDoSDistributed Denial of ServiceDPIDeep Packet InspectionESMTPEnhanced Simple Mail Transfer ProtocolFPGAField Programmable Gate ArrayFSLFast Simplex LinkGbpsGiga-bit per secondGPUGraphical User InterfaceHDLHardware Description LanguageHIDSHost Intrusion Detection SystemHTTPHypertext Transfer ProtocolICIntegrated CircuitICMPInernet ProtocolIPSIntrusion Prevention SystemIPInternet Protocol SecurityIPv4Internet Protocol version 4 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ASIPApplication-Specific Instruction-set ProcessorBGPBorder Gateway ProtocolBMBoyer-MooreBRAMBlock Random Access MemoryCAMContent Addressable MemoryCERTComputer Emergency Response TeamCIACComputer Incident Advisory CapabilityCPUCentral Processing UnitDEHADecision Engine Hardware AcceleratorDoSDenial of ServiceDDoSDistributed Denial of ServiceDPIDeep Packet InspectionESMTPEnhanced Simple Mail Transfer ProtocolFPGAField Programmable Gate ArrayFSLFast Simplex LinkGbpsGiga-bit per secondGPUGraphical User InterfaceHDLHardware Description LanguageHIDSHost Intrusion Detection SystemHTTPHypertext Transfer ProtocolICIntegrated CircuitICMPInernet Control Message ProtocolIDSIntrusion Detection SystemIPInternet ProtocolIPSIntrusion Prevention SystemIPInternet Protocol Security                                         |

| BGPBorder Gateway ProtocolBMBoyer-MooreBRAMBlock Random Access MemoryCAMContent Addressable MemoryCERTComputer Emergency Response TeamCIACComputer Incident Advisory CapabilityCPUCentral Processing UnitDEHADecision Engine Hardware AcceleratorDoSDenial of ServiceDDoSDistributed Denial of ServiceDPIDeep Packet InspectionESMTPEnhanced Simple Mail Transfer ProtocolFPGAField Programmable Gate ArrayFSLFast Simplex LinkGbpsGiga-bit per secondGPUGraphical User InterfaceHDLHardware Description LanguageHIDSHost Intrusion Detection SystemHTTPHypertext Transfer ProtocolICIntegrated CircuitICMPInernet Control Message ProtocolIDSIntrusion Detection SystemIPInternet ProtocolIPSIntrusion Prevention SystemIPSIntrusion Prevention SystemIPSInternet Protocol Security                                                            |

| BMBoyer-MooreBRAMBlock Random Access MemoryCAMContent Addressable MemoryCERTComputer Emergency Response TeamCIACComputer Incident Advisory CapabilityCPUCentral Processing UnitDEHADecision Engine Hardware AcceleratorDoSDenial of ServiceDDoSDistributed Denial of ServiceDPIDeep Packet InspectionESMTPEnhanced Simple Mail Transfer ProtocolFPGAField Programmable Gate ArrayFSLFast Simplex LinkGbpsGiga-bit per secondGPUGraphic Processing UnitGUIGraphical User InterfaceHDLHardware Description LanguageHIDSHost Intrusion Detection SystemHTTPHypertext Transfer ProtocolICIntegrated CircuitICMPInernet ProtocolIPIntrusion Prevention SystemIPIntrusion Prevention SystemIPSIntrusion Prevention SystemIPSecInternet Protocol Security                                                                                              |

| BRAMBlock Random Access MemoryCAMContent Addressable MemoryCERTComputer Emergency Response TeamCIACComputer Incident Advisory CapabilityCPUCentral Processing UnitDEHADecision Engine Hardware AcceleratorDoSDenial of ServiceDDoSDistributed Denial of ServiceDPIDeep Packet InspectionESMTPEnhanced Simple Mail Transfer ProtocolFPGAField Programmable Gate ArrayFSLFast Simplex LinkGbpsGiga-bit per secondGPUGraphical User InterfaceHDLHardware Description LanguageHIDSHost Intrusion Detection SystemHTTPHypertext Transfer ProtocolICIntegrated CircuitICMPInernet ProtocolIPSIntrusion Prevention SystemIPInternet ProtocolIPSIntrusion Prevention SystemIPsecInternet Protocol Security                                                                                                                                              |

| CAMContent Addressable MemoryCERTComputer Emergency Response TeamCIACComputer Incident Advisory CapabilityCPUCentral Processing UnitDEHADecision Engine Hardware AcceleratorDoSDenial of ServiceDDoSDistributed Denial of ServiceDPIDeep Packet InspectionESMTPEnhanced Simple Mail Transfer ProtocolFPGAField Programmable Gate ArrayFSLFast Simplex LinkGbpsGiga-bit per secondGPUGraphical User InterfaceHDLHardware Description LanguageHIDSHost Intrusion Detection SystemHTTPHypertext Transfer ProtocolICIntegrated CircuitICMPIncrnet ProtocolIPInternet ProtocolIPSIntrusion Detection SystemIPInternet ProtocolIPSIntrusion Prevention SystemIPSIntrusion Prevention SystemIPSecInternet Protocol Security                                                                                                                            |

| CERTComputer Emergency Response TeamCIACComputer Incident Advisory CapabilityCPUCentral Processing UnitDEHADecision Engine Hardware AcceleratorDoSDenial of ServiceDDoSDistributed Denial of ServiceDPIDeep Packet InspectionESMTPEnhanced Simple Mail Transfer ProtocolFPGAField Programmable Gate ArrayFSLFast Simplex LinkGbpsGiga-bit per secondGPUGraphical User InterfaceHDLHardware Description LanguageHIDSHost Intrusion Detection SystemHTTPHypertext Transfer ProtocolICIntegrated CircuitICMPInernet ProtocolIDSIntrusion Detection SystemIPInternet ProtocolIPSIntrusion Prevention SystemIPSIntrusion Prevention SystemIPsecInternet Protocol Security                                                                                                                                                                            |

| CIACComputer Incident Advisory CapabilityCPUCentral Processing UnitDEHADecision Engine Hardware AcceleratorDoSDenial of ServiceDDoSDistributed Denial of ServiceDPIDeep Packet InspectionESMTPEnhanced Simple Mail Transfer ProtocolFPGAField Programmable Gate ArrayFSLFast Simplex LinkGbpsGiga-bit per secondGPUGraphical User InterfaceHDLHardware Description LanguageHIDSHost Intrusion Detection SystemHTTPHypertext Transfer ProtocolICIntegrated CircuitICMPInernet Control Message ProtocolIDSIntrusion Detection SystemIPInternet ProtocolIPSIntrusion Prevention SystemIPSIntrusion Prevention SystemIPSIntrusion Prevention SystemIPSIntrusion Prevention SystemIPSIntrusion Prevention System                                                                                                                                     |

| CPUCentral Processing UnitDEHADecision Engine Hardware AcceleratorDoSDenial of ServiceDDoSDistributed Denial of ServiceDPIDeep Packet InspectionESMTPEnhanced Simple Mail Transfer ProtocolFPGAField Programmable Gate ArrayFSLFast Simplex LinkGbpsGiga-bit per secondGPUGraphic Processing UnitGUIGraphical User InterfaceHDLHardware Description LanguageHIDSHost Intrusion Detection SystemHTTPHypertext Transfer ProtocolICIntegrated CircuitICMPInernet ProtocolIPSIntrusion Prevention SystemIPInternet ProtocolIPSIntrusion Prevention SystemIPSInternet Protocol Security                                                                                                                                                                                                                                                              |

| DEHADecision Engine Hardware AcceleratorDoSDenial of ServiceDDoSDistributed Denial of ServiceDPIDeep Packet InspectionESMTPEnhanced Simple Mail Transfer ProtocolFPGAField Programmable Gate ArrayFSLFast Simplex LinkGbpsGiga-bit per secondGPUGraphic Processing UnitGUIGraphical User InterfaceHDLHardware Description LanguageHIDSHost Intrusion Detection SystemHTTPHypertext Transfer ProtocolICIntegrated CircuitICMPInternet ProtocolIDSIntrusion Detection SystemIPIntrusion Detection SystemIPInternet ProtocolIPSIntrusion Prevention SystemIPSIntrusion Prevention SystemIPSIntrusion Prevention SystemIPSInternet Protocol Security                                                                                                                                                                                                |

| DoSDenial of ServiceDDoSDistributed Denial of ServiceDPIDeep Packet InspectionESMTPEnhanced Simple Mail Transfer ProtocolFPGAField Programmable Gate ArrayFSLFast Simplex LinkGbpsGiga-bit per secondGPUGraphic Processing UnitGUIGraphical User InterfaceHDLHardware Description LanguageHIDSHost Intrusion Detection SystemHTTPHypertext Transfer ProtocolICIntegrated CircuitICMPInernet Control Message ProtocolIDSIntrusion Detection SystemIPInternet ProtocolIPSIntrusion Prevention SystemIPSecInternet Protocol Security                                                                                                                                                                                                                                                                                                               |

| DDoSDistributed Denial of ServiceDPIDeep Packet InspectionESMTPEnhanced Simple Mail Transfer ProtocolFPGAField Programmable Gate ArrayFSLFast Simplex LinkGbpsGiga-bit per secondGPUGraphic Processing UnitGUIGraphical User InterfaceHDLHardware Description LanguageHIDSHost Intrusion Detection SystemHTTPHypertext Transfer ProtocolICIntegrated CircuitICMPInernet Control Message ProtocolIDSIntrusion Detection SystemIPInternet ProtocolIPInternet ProtocolIPSIntrusion Prevention SystemIPSIntrusion Prevention SystemIPSInternet Protocol Security                                                                                                                                                                                                                                                                                    |

| DPIDeep Packet InspectionESMTPEnhanced Simple Mail Transfer ProtocolFPGAField Programmable Gate ArrayFSLFast Simplex LinkGbpsGiga-bit per secondGPUGraphic Processing UnitGUIGraphical User InterfaceHDLHardware Description LanguageHIDSHost Intrusion Detection SystemHTTPHypertext Transfer ProtocolICIntegrated CircuitICMPInernet Control Message ProtocolIDSIntrusion Detection SystemIPInternet ProtocolIPSIntrusion Prevention SystemIPSIntrusion Prevention SystemIPsecInternet Protocol Security                                                                                                                                                                                                                                                                                                                                      |

| ESMTPEnhanced Simple Mail Transfer ProtocolFPGAField Programmable Gate ArrayFSLFast Simplex LinkGbpsGiga-bit per secondGPUGraphic Processing UnitGUIGraphical User InterfaceHDLHardware Description LanguageHIDSHost Intrusion Detection SystemHTTPHypertext Transfer ProtocolICIntegrated CircuitIDSInternet Control Message ProtocolIDSIntrusion Detection SystemIPInternet ProtocolIPInternet ProtocolIPSIntrusion Prevention SystemIPsecInternet Protocol Security                                                                                                                                                                                                                                                                                                                                                                          |

| FPGAField Programmable Gate ArrayFSLFast Simplex LinkGbpsGiga-bit per secondGPUGraphic Processing UnitGUIGraphical User InterfaceHDLHardware Description LanguageHIDSHost Intrusion Detection SystemHTTPHypertext Transfer ProtocolICIntegrated CircuitICMPInernet Control Message ProtocolIDSIntrusion Detection SystemIPInternet ProtocolIPInternet ProtocolIPSIntrusion Prevention SystemIPsecInternet Protocol Security                                                                                                                                                                                                                                                                                                                                                                                                                     |

| FSLFast Simplex LinkGbpsGiga-bit per secondGPUGraphic Processing UnitGUIGraphical User InterfaceHDLHardware Description LanguageHIDSHost Intrusion Detection SystemHTTPHypertext Transfer ProtocolICIntegrated CircuitICMPInernet Control Message ProtocolIDSIntrusion Detection SystemIPInternet ProtocolIPSIntrusion Prevention SystemIPSIntrusion Prevention SystemIPsecInternet Protocol Security                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| GbpsGiga-bit per secondGPUGraphic Processing UnitGUIGraphical User InterfaceHDLHardware Description LanguageHIDSHost Intrusion Detection SystemHTTPHypertext Transfer ProtocolICIntegrated CircuitICMPInernet Control Message ProtocolIDSIntrusion Detection SystemIPInternet ProtocolIPInternet ProtocolIPSIntrusion Prevention SystemIPsecInternet Protocol Security                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| GPUGraphic Processing UnitGUIGraphical User InterfaceHDLHardware Description LanguageHIDSHost Intrusion Detection SystemHTTPHypertext Transfer ProtocolICIntegrated CircuitICMPInernet Control Message ProtocolIDSIntrusion Detection SystemIPInternet ProtocolIPSIntrusion Prevention SystemIPsecInternet Protocol Security                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| GUIGraphical User InterfaceHDLHardware Description LanguageHIDSHost Intrusion Detection SystemHTTPHypertext Transfer ProtocolICIntegrated CircuitICMPInernet Control Message ProtocolIDSIntrusion Detection SystemIPInternet ProtocolIPSIntrusion Prevention SystemIPsecInternet Protocol Security                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| HDLHardware Description LanguageHIDSHost Intrusion Detection SystemHTTPHypertext Transfer ProtocolICIntegrated CircuitICMPInernet Control Message ProtocolIDSIntrusion Detection SystemIPInternet ProtocolIPSIntrusion Prevention SystemIPsecInternet Protocol Security                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| HIDSHost Intrusion Detection SystemHTTPHypertext Transfer ProtocolICIntegrated CircuitICMPInernet Control Message ProtocolIDSIntrusion Detection SystemIPInternet ProtocolIPSIntrusion Prevention SystemIPsecInternet Protocol Security                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| HTTPHypertext Transfer ProtocolICIntegrated CircuitICMPInernet Control Message ProtocolIDSIntrusion Detection SystemIPInternet ProtocolIPSIntrusion Prevention SystemIPsecInternet Protocol Security                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| ICIntegrated CircuitICMPInernet Control Message ProtocolIDSIntrusion Detection SystemIPInternet ProtocolIPSIntrusion Prevention SystemIPsecInternet Protocol Security                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| ICMPInernet Control Message ProtocolIDSIntrusion Detection SystemIPInternet ProtocolIPSIntrusion Prevention SystemIPsecInternet Protocol Security                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| IDSIntrusion Detection SystemIPInternet ProtocolIPSIntrusion Prevention SystemIPsecInternet Protocol Security                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| IPInternet ProtocolIPSIntrusion Prevention SystemIPsecInternet Protocol Security                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| IPSIntrusion Prevention SystemIPsecInternet Protocol Security                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| IPsec Internet Protocol Security                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| ů l                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| IPv4 Internet Protocol version 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| IPv6 Internet Protocol version 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| IRC Internet Relay Chat                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| ISP Internet Service Provider                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| LMB Local Memory Bus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| MAC Media Acess Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| MIT Massachusetts Institute of Technology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| NIDS            | Network Intrusion Prevention System                                                                  |

|-----------------|------------------------------------------------------------------------------------------------------|

| NPU             | Netwok Processing Unit                                                                               |

| OPB             | On-chip Peripheral Bus                                                                               |

| OS              | Operating System                                                                                     |

| OSPF            | Open Shortest Path First                                                                             |

| OTN             | Option Tree Node                                                                                     |

| P2P             | Peer-to-Peer                                                                                         |

| PCHA            | Packet Capture Hardware Accelerator                                                                  |

| PMHA            | Pattern Matching Hardware Accelerator                                                                |

| POD             | Ping of Death                                                                                        |

| PCRE            | Perl Compatible Regular Expressions                                                                  |

| $\mathbf{QoS}$  | Quality of Service                                                                                   |

| $\mathbf{RAM}$  | $ \mathbf{R} \mathbf{andom} \ \mathbf{A} \mathbf{ccess} \ \mathbf{M} \mathbf{emory} $                |

| RISC            | Reduced Instruction Set Computer                                                                     |

| $\mathbf{RPC}$  | Remote Procedure Call                                                                                |

| $\mathbf{RTN}$  | $\mathbf{R}$ ule $\mathbf{T}$ ree $\mathbf{N}$ ode                                                   |

| <b>SB-NIDS</b>  | Signature Based-Network Intrusion Detection System                                                   |

| <b>SB-NIPS</b>  | Signature Based-Network Intrusion Prevention System                                                  |

| SDRAM           | $\mathbf{S}$ ynchronous $\mathbf{D}$ ynamic $\mathbf{R}$ andom $\mathbf{A}$ ccess $\mathbf{M}$ emory |

| $\mathbf{SIP}$  | Session Initiation Protocol                                                                          |

| SMTP            | Simple Mail Transfer Protocol                                                                        |

| $\mathbf{SoC}$  | System on Chip                                                                                       |

| SoPC            | $\mathbf{S}$ ystem on $\mathbf{P}$ rogrammable $\mathbf{C}$ hip                                      |

| $\mathbf{SPI}$  | Stateful Packet Inspection                                                                           |

| $\mathbf{SRAM}$ | Static Random Access Memory                                                                          |

| $\mathbf{SRT}$  | Snort Rule Tree                                                                                      |

| $\mathbf{SSL}$  | Secure Socket Layer                                                                                  |

| TCP             | Transmission Control Protocol                                                                        |

| $\mathbf{TFN}$  | Tribe Flood Network                                                                                  |

| $\mathbf{ToS}$  | $\mathbf{T}$ ype of Service                                                                          |

| $\mathbf{TTL}$  | Time to live                                                                                         |

| UDP             | User Datagram Protocol                                                                               |

| US-CERT         | United States-Computer Emergency Readiness Team                                                      |

| VoIP            | Voice over Internet Protocol                                                                         |

|                 |                                                                                                      |

# Chapter 1

# Introduction

This thesis is about optimisation of Signature-based Network Intrusion Detection System (SB-NIDS) packet analysis speed. A complete SB-NIDS prototype is presented, developed using hybrid hardware-software embedded processing platform.

## 1.1 Background and Problem Overview

One of the effective ways to secure computer networks from the attacks is the network defence software technology such as Network Intrusion Detection System (NIDS). NIDS has been widely adopted in the business and government sector to secure computer networks by detecting different kinds of network attack as well as detection of illegal access to confidential data and resources. Although NIDS is a good network defence software, on high data rate networks such as gigabit rate its performance is poor. It is unable to analyse all traffic as network packets arrive faster than NIDS packet analysis speed. Consequently, NIDS packet buffer fills very quickly and force it to drop some packets without analysis in order to make more space in buffer for new packets. For example, SB-NIDS software package Snort when executed on Intel Xeon Dual-Core 2.0 GHz general purpose processor and test with network test data which requires 175 concurrent Transmission Control Protocol (TCP) connections is only able to analyse network traffic up to 566 Mbps throughput [2, 3]. The main reasons for slow packet analysis rate are the complexity of network packet analysis operations and frequent memory accesses. These operations typically involve bit masking, bit comparison, bit shifting that general purpose processor instruction sets do not support efficiently. Also frequent memory accesses on these loosely coupled processor architectures consume a relatively high number of CPU clock cycles (100s) if a cache miss occurs (Section 6.3).

Various attempts have been made to optimise SB-NIDS packet analysis speed (Chapter 3). Most of the current state of the art solutions optimise only specific computationally intensive parts or components of SB-NIDS software (Section 3.5). Some solutions use clusters of processors and high performance embedded processing platforms in order to optimise a complete SB-NIDS application (Section 3.4.1). Commercial NIDS solutions based on embedded processing platforms use high specification embedded processing hardware. They claim to provide a complete SB-NIDS solutions with a support of up to 10 Gbps network throughput (Section 2.4.5). Still a great deal of work needed to be done to support NIDS packet analysis throughput preferably over 10 gigabit rate as network data rates continuously increasing such as recently approved IEEE 802.3ba standard which supports 40 Gbps and 100 Gbps transmission rate [4].

# 1.2 Solution Synopsis

A prototype SB-NIDS using hybrid hardware-software embedded processing platform was developed to enable high speed packet analysis. To support this effort, an open source and widely used SB-NIDS software package Snort was used. An execution analysis of Snort was carried out using software profiling tools in order to identify bottlenecks in packet analysis. Based on the profiling results, the most suitable embedded processing platform was selected. This embedded platform is a hybrid hardware-software processing solution having tightly coupled hardware architecture to enable low clock cycle accesses to hardware peripherals such as Network Interface Cards (NICs) and memory. It also allows hardware accelerator development in Field Programmable Gate Array (FPGA) and multi-processing using MicroBlaze soft processing cores. One of the main goals of hardware accelerator development is to offload any computationally significant operation of a software from a CPU to FPGA. FPGA provides parallelism, pipelining and bitlevel processing facility, and has great potential to reduce and/or remove performance bottlenecks in SB-NIDS software. Multi-processing facility can be applied to SB-NIDS packet analysis process in order to improve the overall SB-NIDS processing efficiency although this is not investigated in this thesis.

Prototyping and optimisation was carried out in stages. Initially, Snort was ported to the embedded processing platform. This involved Snort software architecture restructuring in order to successfully map and execute to new processing platform which is based on Xilinx MicroBlaze soft-core processor and FPGA. This prototype is called as Manchester Metropolitan University-Snort I (MMU-Snort I). MMU-Snort I performance on new processing platform then evaluated to identify any improvement or bottlenecks in packet analysis processes. Test results showed that prototype SB-NIDS or MMU-Snort I execution speed has improved when compared with the CPU clock cycles of the original Snort software package when executed on a PC with a general purpose processor.

In the next stage pattern matching algorithm performance was optimised. This involved development of Pattern Matching Hardware Accelerator (PMHA) and its integration into Snort prototype or MMU-Snort I. This resulted in the second prototype called MMU-Snort II. PMHA provides high throughput and low memory pattern matching solution using a Bloom filter data structure based approach which allows quick lookup of keywords or patterns [5]. The size of the attack signatures is significantly reduced to the extent that the whole attack pattern represented as Bloom filter is stored to FPGA on-chip memory/Block Random Access Memory (BRAM) for quick checking of signature presence in packet payload data. Additionally, full database of patterns is stored in off-chip Synchronous Dynamic Random Access Memory (SDRAM) for further signature checking in case a signature stored in FPGA BRAM is found in a packet during first stage of pattern lookup. This is because Bloom filter search approach can provide false positive matches for pattern lookup. The integration of PMHA into MMU-Snort I required further design changes, resulting in an optimised and integrated PMHA for Snort on the same processing platform. In the last stage, PMHA was further optimised to search efficiently longer patterns (> 64 Bytes) and for fast pruning of Bloom filter false positive matches which resulted in MMU-Snort III prototype.

In summary, investigation and development of complete SB-NIDS prototype using hybrid hardware-software processing platform is presented here, with a focus on the added benefits of throughput and reduced memory requirements. A full description of the architectures and algorithms is presented in this thesis. In addition, a detailed performance analysis and experimental results are used to demonstrate the suitability of hybrid hardware-software platform for SB-NIDS execution, higher throughput support and smaller memory requirements.

# **1.3** Aims and Objectives

The aim of this research project is to develop a series of algorithms and hardware architectures for SB-NIDS in order to optimise its packet analysis speed.

## 1.3.1 Objectives

In order to achieve this aim; following research objectives have been identified:

- Design and implement SB-NIDS prototype that perform network packet analysis at higher speed than Snort on general purpose processor.

- Evaluate SB-NIDS prototype using publicly available data for SB-NIDS testing and identify packet analysis speed improvement and/or any performance issues.

- Gain efficiency and/or improve SB-NIDS packet analysis speed by offloading pattern matching from CPU to FPGA that search one of the largest attack patterns preferably at gigabit data rate.

- Use Snort application specific knowledge (Section 5.2.2) to improve pattern matching (PMHA) performance further by reducing number of pattern search per packet.

- Evaluate PMHA implementation using publicly available test data for SB-NIDS in order to to verify its performance improvement.

# **1.4** Contributions and Claims

The primary objective of this effort is the development of SB-NIDS prototype solution using one of the viable embedded hybrid hardware-software processing platforms. The main challenge faced in the development on this platform is the design and implementation of a full SB-NIDS while improving the performance needed by the state of the art networks of today. This embedded processing platform is flexible as it not only allows the execution of complete software applications such as SB-NIDS on an embedded processor but also supports software optimisation, and enables the offloading of processing from a CPU to FPGA hardware and multi-processing with multiple processing cores. It also enables overall improvements in packet analysis speed of SB-NIDS due to tightly coupled hardware architecture in which hardware peripherals like Ethernet network interface have significantly lower latency access to network data and the CPU performs relatively fast off-chip memory accesses requiring tens of clock cycles in comparison to hundreds of clock cycles on general purpose processor architectures. The platform memory hierarchy arrangement in low-to-high clock cycles memory access sort order are, FPGA BRAM, off-chip Static Random Access Memory (SRAM) and off-chip Synchronous Dynamic Random Access Memory (SDRAM). This allows further improvements in the SB-NIDS performance by storing frequently access data such as network attack patterns or signatures to low latency access memory. Overall the processing platform features is found to be viable to implement the SB-NIDS. Also, flexible hybrid hardware-software processing and scalability in terms of multiple processing cores are ideal for further optimisation of other SB-NIDS components that are bottlenecks on high speed packet analysis. The idea presented in this thesis is a prototype SB-NIDS solution

that is intended to demonstrate the suitability of hybrid hardware-software processing for SB-NIDS execution, optimisation and further research and development.